2D products are normally made at temperature levels that damage silicon chips.

Think it or not, this portion of mineral consists of great deals of private layers that are atomically thin.

Credit: Kwisky

Silicon chip producers like Intel and TSMC are continuously outshining themselves to make ever smaller sized functions, however they are getting closer to the physical limitations of silicon.

“We currently have really, really high density in silicon-based architectures where silicon efficiency breaks down greatly,” stated Ki Seok Kim, a researcher operating at the Massachusetts Institute of Technology’s Research Laboratory of Electronics.

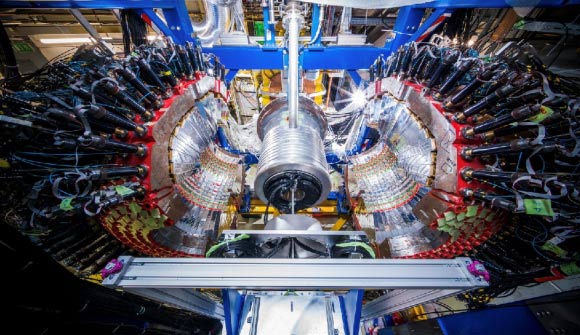

One method around this issue is to change silicon with graphene-like 2D products that keep their semiconducting homes even at a single-atom scale. Another method is developing 3D chips, which squeeze more transistors into the very same location without making transistors smaller sized. Kim’s group did both, developing a 3D chip out of vertically stacked 2D semiconductors.

Being available in hot

Graphene, a single-atom-thin sheet of carbon, is most likely the most well-known 2D product, however it’s not a semiconductor. There are 2D products that are great semiconductors, however, like molybdenum disulfide or tungsten diselenide. “They use extremely steady electrical efficiency even listed below one nanometer,” Kim stated. Both molybdenum disulphide and tungsten diselenide come from a group called shift metal dichalcogenides (TMDs).

These products are normally grown through a procedure called chemical vapor deposition, where vaporized products are sprayed over a substrate and type single-atom-thin crystalline structures on its surface area. To make decently carrying out transistors, those TMDs needed to be transferred at temperature levels reaching 900º Celsius. That was great if you desired simply one layer of transistors, however it isn’t suitable with typical silicon fabrication methods.

The chip production procedure begins with a round silicon wafer. Transistors are made on those wafers straight and form the bottom layer of a chip in a part of the chip fabrication procedure called the front end of line. The very first layer of metal electrical wiring, or interconnects, is then included on top of the transistor layer; this is called the back end of line.

If you wished to include a layer of TMD transistors on top of the back end of line to construct a 3D stacked chip, you ‘d require to warm the entire thing to 900 ° Celsius, which would generally fry the circuitry. Scientists checking out structure 3D chips proposed numerous options to this circuitry-frying issue, however none appeared to work especially well.

The most popular technique was a procedure called the through-silicon-via (TSV), which was utilized to make layers of transistors on different silicon wafers with drilled tiny holes to link the upper wafer with the bottom wafer. The procedure was extremely costly, and lining up the wafers thoroughly enough to link nanometer-scale gadgets was an obstacle. An option was to move transistors grown on a different wafer, which fixed the hole-drilling problem however left the positioning issue.

Researchers likewise attempted to do chemical vapor deposition of TMDs at temperature levels listed below 400 ° Celsius, which was thought about safe for the metal circuits. At these low temperature levels, TMDs formed poly-crystalline products rather of single-crystal structures, which substantially deteriorated their electrical efficiency.

“The objective was to deposit single-crystalline TMD transistors straight on top of the back end of line in temperature levels listed below 400 ° Celsius,” Kim stated. “This is precisely what we have actually attained.”

Nanoscale metallurgy

The service proposed by Kim’s group was influenced by metallurgy. When a molten metal is put into a mold, it gradually forms what are called nuclei: grains of strong product that combine to produce routine crystal patterns that even more solidify into strong type. Kim and his coworkers discovered that this nucleation procedure normally began at the edges of the mold. “Nucleating at the edges needs less energy and heat,” Kim stated. The scientists obtained this idea and utilized it to produce single-crystalline TMD transistors. They called this strategy “geometric confinement.”

Much like with basic chip production, the procedure began with a silicon wafer, which was then covered with a thin insulator layer of hafnium oxide. Layer, the group included a polymer finish. That polymer layer was then formed into trenches– rectangle-shaped pockets that were then covered with silicon dioxide. Tungsten diselenide vapor was sprayed over this selection of trenches at 485 ° C as part of the chemical vapor deposition procedure. This is where the magic took place.

Usually, formation forms a polycrystalline product. In a nucleation occasion, a single-crystalline structure is formed, however as the procedure goes on, a 2nd nucleation website will quickly form, and after that another, till the entire bulk of product ends up being taken shape. The crystalline structures formed in each of those nucleation occasions are separated by grain borders, the signature of a polycrystalline product.

Kim’s group fine-tuned the size of the trenches so that the whole trench might be filled with a crystalline structure formed in a single nucleation occasion. The condensation in each trench began with a nucleation occasion at its edge, simply as it would in metal molds. The crystalline structure then filled the trench and lacked readily available area right before the 2nd nucleation occasion might occur.

This formed the very first single-crystalline 2D semiconducting layer, which was then become transistors by transferring platinum source and drain areas topped with eviction and separated with another layer of hafnium oxide. That finished the very first back end of line.

The 2nd layer of transistors was grown straight on top of the very first one utilizing the exact same procedure, with 2 distinctions. The semiconducting TMD was molybdenum disulfide, which might be transferred at 385 ° C, and the product utilized for source and drain areas was chromium. “The electrical efficiency we attained was exceptional, comparable to high-temperature grown TMDs. We showed monolithic, vertically stacked CMOS made with single-crystalline TMDs at listed below 400 ° C temperature level for the very first time,” Kim stated.

Getting the temperature level of TMDs development down enough to make massive production practical might be a big leap towards making 3D stacked CMOS with 2D semiconductors in real items individuals can utilize. 5 members of Kim’s group operated at Samsung’s Device Research Center in South Korea, which may make it appear like we’re on the brink of getting this innovation to market. The issue is that we require a minimum of another comparable leap before we bid farewell to silicon chips.

Doping issue

Presently, we do not understand how to link TMD semiconductors with other gadgets. In today’s chips, connections are attained by doping: injecting the silicon with pollutants to increase its conductivity exactly at points where it interfaces with metal electrical wiring. Those injected pollutants ravel the conductivity drop when the signal is moving in between semiconductors and extremely conductive products like chromium, copper, or platinum.

At an atomic scale, doping replacements atoms of a host metal with foreign atoms. How do you do that when your host product is one atom thin?

There have actually been efforts to attain results rather comparable to doping in 2D molybdenum disulphide, however the procedure was challenging to manage. In Kim’s paper, the group composed that establishing a doping procedure for TMDs that can be done listed below 400 ° Celsius is required to construct high-performing chips based upon 2D semiconductors. The group believes its innovation might assist in growing drugged TMDs, however up until now, we have no chance to do so.

Another looming concern is cooling. Getting the heat out of a very largely jam-packed chip is hard adequate with a single layer of transistors. Stacking numerous such layers on top of each other ought to make the problem significantly even worse. “A heat sink location is required in gadgets like that. This is likewise something we prepare to do in the future– establishing a brand-new cooling plan for such chips,” Kim stated.

Kim argues that these difficulties are worth dealing with, as he feels 3D stacked chips based on 2D semiconductors will drastically increase the efficiency we can get out of the very same chip location and substantially lower the power usage compared to basic CMOS electronic devices. And all that will be required for powering future AI systems.

“We will attain really, extremely high-density AI chips,” Kim stated.

Nature, 2024. DOI: 10.1038/ s41586-024-08236-9

Jacek Krywko is a freelance science and innovation author who covers area expedition, expert system research study, computer technology, and all sorts of engineering wizardry.

13 Comments

Find out more

As an Amazon Associate I earn from qualifying purchases.